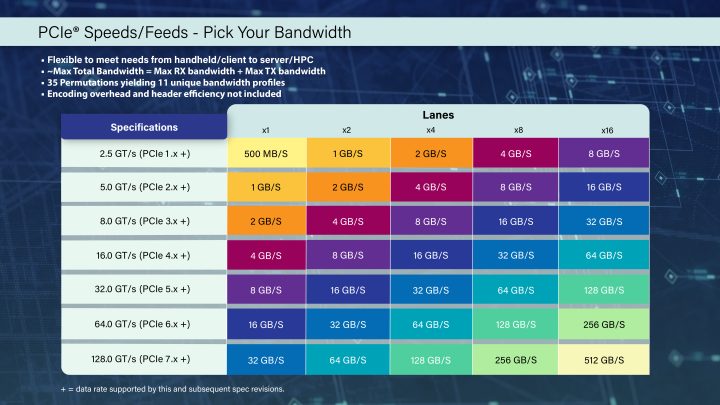

PCI-SIG on Wednesday has announced the PCI Express 7.0 with 128GT/s raw bit rate, data transfer speed of 32GB/s on a single bi-directional connection, and can achieve 512GB/s peak bandwidth on full 16-lane PCIe 7.0 connection.

PCIe 7.0 final specification’s targeted release is in 2025, while initial PCIe 7.0 equipped devices may hit the market around 2027.

The newest PCIe standard will use PAM4 (Pulse Amplitude Modulation with 4 levels) signaling—which was introduced with PCIe 6.0—and this generation focuses on maintaining backwards compatibility with all previous generations of PCIe technology, keeping low latency, and improving power efficiency.

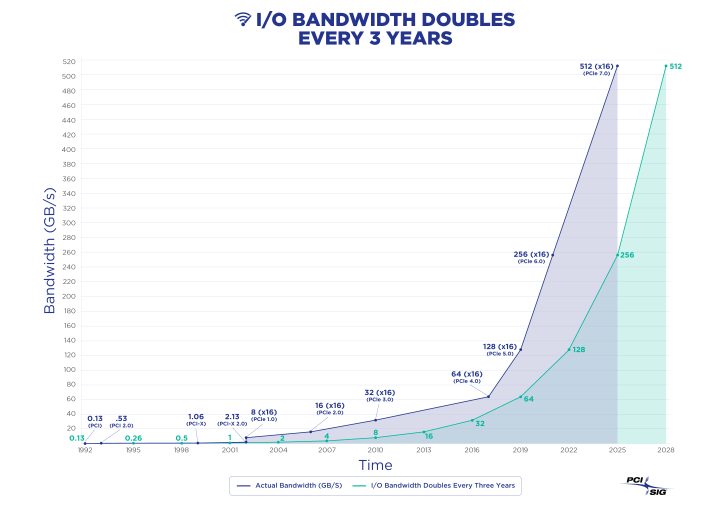

According to PCI-SIG, I/O bandwidth doubles every three years or in other words, every PCIe generation doubles the speed of the previous one. PCIe 5.0 was first demonstrated in 2017 with 128GB/s peak, but only coming to prominence currently with AMD’s next AM5 socket and Intel’s new LGA1700.

While PCIe 6.0 with 256GB/s peak is yet to appear in server parts next year.

PCI-SIG or the Peripheral Component Interconnect Special Interest Group is the consortium who owns PCI specifications and is responsible for developing and maintaining the standardized approach to peripheral component I/O data transfers.

Source (1)

0 Comments

Leave a Reply